## (19) United States

### (12) Patent Application Publication (10) Pub. No.: US 2020/0176655 A1 IGUCHI et al.

Jun. 4, 2020

(43) Pub. Date:

#### (54) IMAGE DISPLAY ELEMENT

(71) Applicant: SHARP KABUSHIKI KAISHA, Sakai City (JP)

(72) Inventors: KATSUJI IGUCHI, Sakai City (JP); TAKASHI KURISU, Sakai City (JP); MASUMI MAEGAWA, Sakai City

Appl. No.: 16/698,715

(22) Filed: Nov. 27, 2019

### Related U.S. Application Data

Provisional application No. 62/773,724, filed on Nov. 30, 2018.

#### **Publication Classification**

(51) Int. Cl. H01L 33/62 (2006.01)H01L 25/075 (2006.01)H01L 33/52 (2006.01)

U.S. Cl. CPC ...... H01L 33/62 (2013.01); H01L 33/52 (2013.01); H01L 25/0753 (2013.01)

#### (57)**ABSTRACT**

In a micro light emitting element, a first metal film electrically connected to a second conductive layer is disposed on a surface on an opposite side of a light emitting surface side. The first metal film covers the second conductive layer. A first inclined angle of a first conductive layer side surface from a slope formed around a light emission layer to the light emitting surface is larger than a second inclined angle of the slope. The slope and the first conductive layer side surface are covered together by a second metal film. A first transparent insulating film is disposed between the slope and the second metal film.

FIG. 4

FIG. 6 (a) (b) O LIGHT EXTRACTION EFFICIENCY OLIGHT EXTRACTION EFFICIENCY **D** AREA RATIO **DAREA RATIO** 100% 100% 90% 30% 0 0 O  $\circ$ 80% 80% Ö õ 0 70% 70% 80% 80% <u></u> 80% S0% 13 40% 40% 30% 30% 20% 20% ۵ 10% 10% 0% (% 75 98 0.5 70 15 INCLINED ANGLE Ob (\*) DEPTH D (um) (c) (d)O LIGHT EXTRACTION EFFICIENCY **OUGHT EXTRACTION EFFICIENCY D** AREA RATIO D AREA RATIO 100% 100% 9%, 90% ¢ 0 80% 80% ō 70% 70% ٥ 80% 80% 3 30% 90% 33 40% 40% 30% 30% 20% 20% 10% 10% 0% L 25 0% , 40 45 50 55 INCLINED ANGLE θe (°) 30 65 THICKNESS OF N-SIDE LAYER 11 (µm) (e) O LIGHT EXTRACTION EFFICIENCY to AREA RATIO 100% 90% 80% 70% 80% 50% 40% 30% 20% 10% 0% 0.2 8.4 08 THICKNESS OF P-SIDE LAYER 13 (μm)

LIGHT EMITTING DIRECTION B K ŭ LIGHT EMITTING SURFACE S

1: PIXEL REGION

3: N CONNECTION REGION 10: P-SIDE METAL LAYER

11: N-SIDE LAYER

11S: N-SIDE LAYER SIDE SURFACE

12: LIGHT EMISSION LAYER

13. P-SIDE LAYER 14: COMPOUND SEMICONDUCTOR

17: TRANSPARENT INSULATING FILM

20N: N-ELECTRODE 20P: P-ELECTRODE

20W: METAL REPLECTIVE LAYER

55: INSULATING FILM

50c: DRIVING CIRCUIT SUBSTRATE

51: P-DRIVE ELECTRODE 52: N-DRIVE ELECTRODE

70: BONDING MATERIAL

100c: MICRO LIGHT-EMITTING ELEMENT

200c: IMAGE DISPLAY ELEMENT

20W: METAL REFLECTIVE LAYER

FIG. 14

FIG. 15

## FIG. 16

# FIG. 17

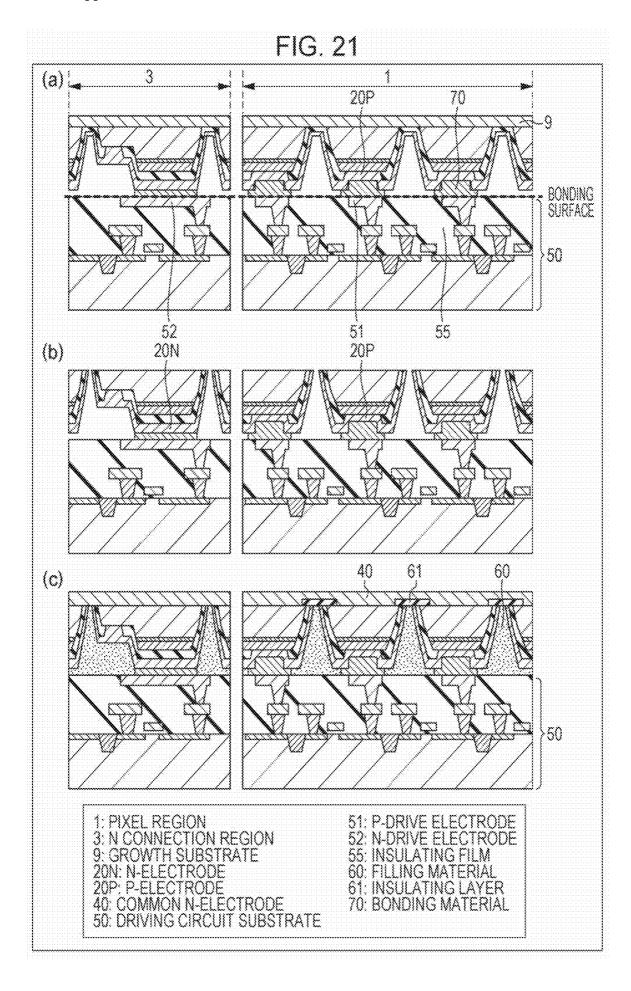

- 1: PIXEL REGION

- 3: N CONNECTION REGION

- 11: N-SIDE LAYER

- 11S: N-SIDE LAYER SIDE SURFACE

- 12: LIGHT EMISSION LAYER

- 13: P-SIDE LAYER

- 14: COMPOUND SEMICONDUCTOR

- 168: SLOPE

- 17. TRANSPARENT INSULATING FILM

- 18: ISOLATION TRENCH

- 20N: N-ELECTRODE

- ZOP: P-ELECTRODE

- 20W: METAL REFLECTIVE LAYER

- 55: INSULATING FILM

- 40: COMMON N-ELECTRODE

- 50: DRIVING CIRCUIT SUBSTRATE

- 61: P-DRIVE ELECTRODE

- 52: N-DRIVE ELECTRODE

- 60: FILLING MATERIAL

- 61: INSULATING LAYER

- 70: BONDING MATERIAL 100h: MICRO LIGHT-EMITTING ELEMENT

- 101h: DUMMY CONNECTION ELEMENT

- 200h: IMAGE DISPLAY ELEMENT

0 T 0 ®

#### IMAGE DISPLAY ELEMENT

#### TECHNICAL FIELD

[0001] The present invention relates to an image display element including a micro light emitting element.

#### BACKGROUND ART

[0002] A display element in which a plurality of micro light emitting elements constituting pixels are arranged in a driving circuit substrate has proposed. For example, in a technology disposed in PTL 1, a driving circuit is formed on a silicon substrate, and a minute light emitting diode (LED) array that emits ultraviolet light is disposed on the driving circuit. Alternatively, the technology discloses a small display element in which a wavelength conversion layer that converts ultraviolet light into visible light of red, green, and blue colors is provided on the light emitting diode array, and thus a color image is displayed.

[0003] Such a display element has characteristics of high luminance and high durability while being small. For this reason, the display element is expected to be a display element for display devices such as glasses-like devices and head-up displays.

[0004] As a manufacturing method of such a display element, a method in which, since the material of the driving circuit substrate is different from the material of the micro light emitting element, the material of the driving circuit substrate and the material of the micro light emitting element are separately formed, and then are stuck to each other is general. Regarding arrangement of an electrode in the micro light emitting element, which has a large influence on the manufacturing method and manufacturing cost, various structures and manufacturing methods thereof are proposed. [0005] For example, a case where electrodes in the micro light emitting element are formed on different surfaces, as disclosed in PTLs 1 and 2, a case where the electrodes in the micro light emitting element are formed on the same surface, as disclosed in PTL 3, or the like is exemplified.

#### CITATION LIST

#### Patent Literature

[0006] [PTL 1] Japanese Unexamined Patent Application Publication No. 2002-141492 (published on May 17, 2002) [0007] [PTL 2] U.S. Patent Application Publication No. 2016/0276329 (published on Sep. 22, 2016)

[0008] [PTL 3] International Publication No. WO2017/094461 (published on Jun. 8, 2017)

#### SUMMARY OF INVENTION

#### Technical Problem

[0009] However, the structure of the micro light emitting element and the display element disclosed in PTLs 1 and 2 described above has problems as follows. Firstly, a large proportion (several tens of percent) of light generated in a light emission layer of the micro light emitting element is emitted from the side surface of the micro light emitting element toward an adjacent micro light emitting element. Such light is absorbed by the adjacent micro light emitting element and is emitted from this micro light emitting element again. Thus, optical crosstalk in which a micro light

emitting element other than a micro light emitting element which is originally to emit light appears to emit light.

[0010] In a case where micro light emitting elements are joined to each other by a compound semiconductor, light is leaked to the adjacent micro light emitting element through the compound semiconductor, and thus similar optical crosstalk occurs. Such optical crosstalk causes a problem of degradation of contrast and degradation of color purity.

[0011] A large quantity of light is lost by light emission from the side surface of the micro light emitting element, and moreover, since light is confined inside the micro light emitting element, a proportion of light to be emitted to the outside to the light generated by the micro light emitting element is decreased, and thus a problem that light emission efficiency is decreased occurs.

[0012] Such decrease of light extraction efficiency is a phenomenon occurring because the refractive index of the compound semiconductor constituting the micro light emitting element is larger than refractive indices of air and resin. A problem of an increase of power consumption and an increase of a temperature by heat generation occurs by decreasing the light emission efficiency.

[0013] An aspect of the present invention has been made considering the above-described problems. An object of the present invention is to prevent the degradation of contrast and the degradation of color purity by preventing the occurrence of optical crosstalk between micro light emitting elements adjacent to each other, and is to reduce power consumption by improving the light emission efficiency of the micro light emitting element.

#### Solution to Problem

[0014] To solve the above problems, (1) according to an embodiment of the present invention, a micro light emitting element includes a compound semiconductor in which a first conductive layer, a light emission layer, and a second conductive layer having a conductivity type opposite to a conductivity type of the first conductive layer are stacked in order from a light emitting surface side. A first metal film electrically connected to the second conductive layer is disposed on a surface on an opposite side of the light emitting surface side. The first metal film covers the second conductive layer. A slope is formed around the light emission layer. A first inclined angle of a first conductive layer side surface from the slope to the light emitting surface is larger than a second inclined angle of the slope. The slope and the first conductive layer side surface are covered together by a second metal film. A first transparent insulating film is disposed between the slope and the second metal film. [0015] (2) According to the embodiment of the present invention, in the micro light emitting element, a second transparent insulating film is disposed between the first conductive layer side surface and the second metal film, in addition to the configuration of (1).

[0016] (3) According to the embodiment of the present invention, in the micro light emitting element, the second transparent insulating film is obtained by the first transparent insulating film extending between the first conductive layer side surface and the second metal film, in addition to the configuration of (2).

[0017] (4) According to another embodiment of the present invention, a micro light emitting element includes a compound semiconductor in which a first conductive layer, a light emission layer, and a second conductive layer having

a conductivity type opposite to a conductivity type of the first conductive layer are stacked in order from a light emitting surface side. A first metal film electrically connected to the second conductive layer is disposed on a surface on an opposite side of the light emitting surface side. The first metal film covers the second conductive layer. A slope is formed around the light emission layer. The slope extends to the light emitting surface and is covered by a second metal film. A first transparent insulating film is disposed between the slope and the second metal film.

[0018] (5) According to the embodiment of the present invention, in the micro light emitting element, a third transparent insulating film is disposed between the second conductive layer and the first metal film, in addition to the configuration of any of (1) to (4).

[0019] (6) According to the embodiment of the present invention, in the micro light emitting element, in plan view from an opposite side of the light emitting surface side, the second metal film is disposed to overlap the first metal film, in addition to the configuration of any of (1) to (5).

[0020] (7) According to the embodiment of the present invention, in the micro light emitting element, a film thickness of the first transparent insulating film is equal to or more than 75 nm, in addition to the configuration of any of (1) to (6).

[0021] (8) According to the embodiment of the present invention, in the micro light emitting element, the film thickness of the first transparent insulating film is equal to or more than 400 nm, in addition to the configuration of any of (1) to (7).

[0022] (9) According to the embodiment of the present invention, in the micro light emitting element, the second inclined angle is equal to or less than 600, in addition to the configuration of any of (1) to (3).

[0023] (10) According to the embodiment of the present invention, in the micro light emitting element, the second inclined angle is equal to or less than 500, in addition to the configuration of any of (1) to (3).

[0024] (11) According to the embodiment of the present invention, in the micro light emitting element, the first metal film includes a layer containing silver or aluminum as a main component, on the compound semiconductor side, in addition to the configuration of any of (1) to (10).

[0025] (12) According to the embodiment of the present invention, in the micro light emitting element, the second metal film includes a layer containing silver or aluminum as a main component, on the compound semiconductor side, in addition to the configuration of any of (1) to (11).

[0026] (13) According to the embodiment of the present invention, in the micro light emitting element, the first transparent insulating film is an  $\mathrm{SiO}_2$  film, in addition to the configuration of any of (1) to (12).

[0027] (14) According to the embodiment of the present invention, in the micro light emitting element, the first inclined angle is less than 900, in addition to the configuration of any of (1) to (3).

[0028] (15) According to the embodiment of the present invention, in the micro light emitting element, the second metal film is electrically connected to the first conductive layer, in addition to the configuration of any of (1) to (14). [0029] (16) According to the embodiment of the present invention, the micro light emitting element further includes a second electrode electrically connected to the second metal

film, on an opposite side of the light emitting surface side, in addition to the configuration of (15).

[0030] (17) According to the embodiment of the present invention, the micro light emitting element further includes a light emitting surface-side electrode configured from a transparent conductive film electrically connected to the first conductive layer, on a surface of the first conductive layer on the light emitting surface side, in addition to the configuration of any of (1) to (14).

[0031] (18) According to the embodiment of the present invention, an image display element has a pixel region in which micro light emitting elements are arranged on a driving circuit substrate in a two-dimensional array shape, in addition to the configuration of any of (1) to (17). A surface of the micro light emitting element on an opposite side of the light emitting surface side faces a surface of the driving circuit substrate. First driving electrodes for supplying a current to the micro light emitting elements are arranged in a two-dimensional array shape on a surface of the driving circuit substrate in the pixel region. A first electrode and the first driving electrode are connected in a one-to-one relation. [0032] (19) According to the embodiment of the present invention, an image display element has a pixel region in which micro light emitting elements are arranged on a driving circuit substrate in a two-dimensional array shape, in addition to the configuration of (17). A surface of the micro light emitting element on an opposite side of the light emitting surface side faces a surface of the driving circuit substrate. First driving electrodes for supplying a current to the micro light emitting elements are arranged in a twodimensional array shape on a surface of the driving circuit substrate in the pixel region. A first electrode and the first driving electrode are connected in a one-to-one relation. A second driving electrode is disposed on a surface of the driving circuit substrate on an outside of the pixel region. The second driving electrode is electrically connected to the light emitting surface-side electrode.

[0033] (20) According to the embodiment of the present invention, an image display element has a pixel region in which micro light emitting elements are arranged on a driving circuit substrate in a two-dimensional array shape, in addition to the configuration of (16). A surface of the micro light emitting element on an opposite side of the light emitting surface side faces a surface of the driving circuit substrate. First driving electrodes and second driving electrodes for supplying a current to the micro light emitting elements are arranged in a two-dimensional array shape on a surface of the driving circuit substrate in the pixel region. A first electrode and the first driving electrode are connected in a one-to-one relation. The second electrode and the second driving electrode are connected to each other.

#### Advantageous Effects of Invention

[0034] It is possible to prevent the degradation of contrast and the degradation of color purity by preventing the occurrence of optical crosstalk between micro light emitting elements adjacent to each other, and to reduce power consumption by improving the light emission efficiency of the micro light emitting element.

#### BRIEF DESCRIPTION OF DRAWINGS

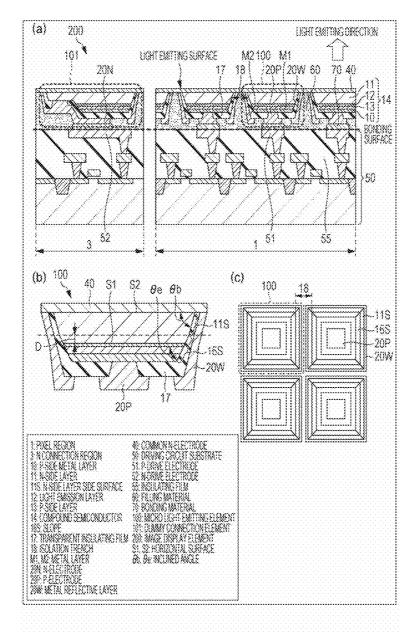

[0035] FIG. 1(a) is a schematic sectional view of an image display element according to Embodiment 1 of the present

invention, FIG.  $\mathbf{1}(b)$  is a schematic sectional view of a micro light emitting element according to Embodiment 1 of the present invention, and FIG.  $\mathbf{1}(c)$  is a schematic plan view of the micro light emitting element according to Embodiment 1 of the present invention.

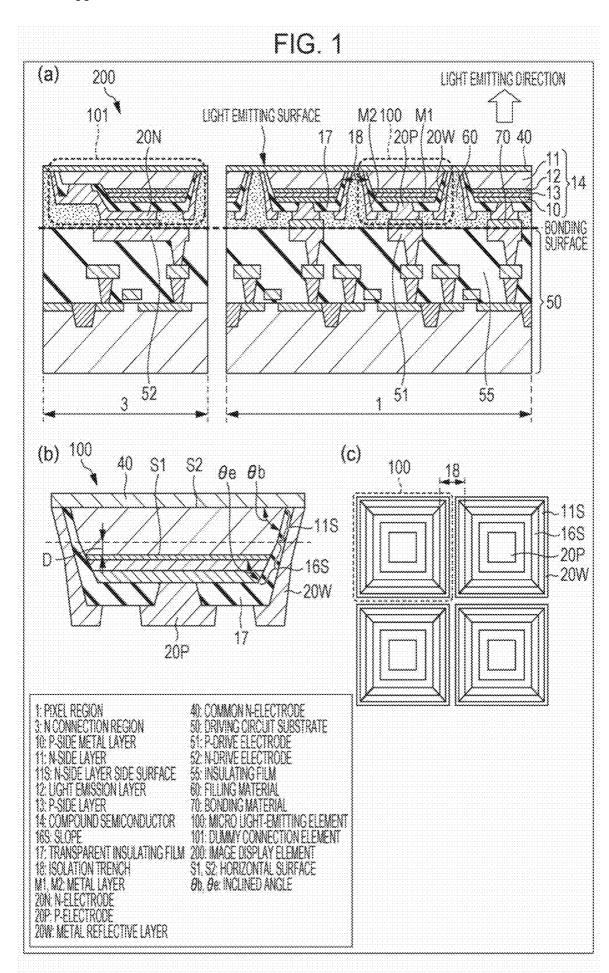

[0036] FIGS. 2(a) to (g) are schematic sectional views illustrating a manufacturing flow of the micro light emitting element according to Embodiment 1 of the present invention

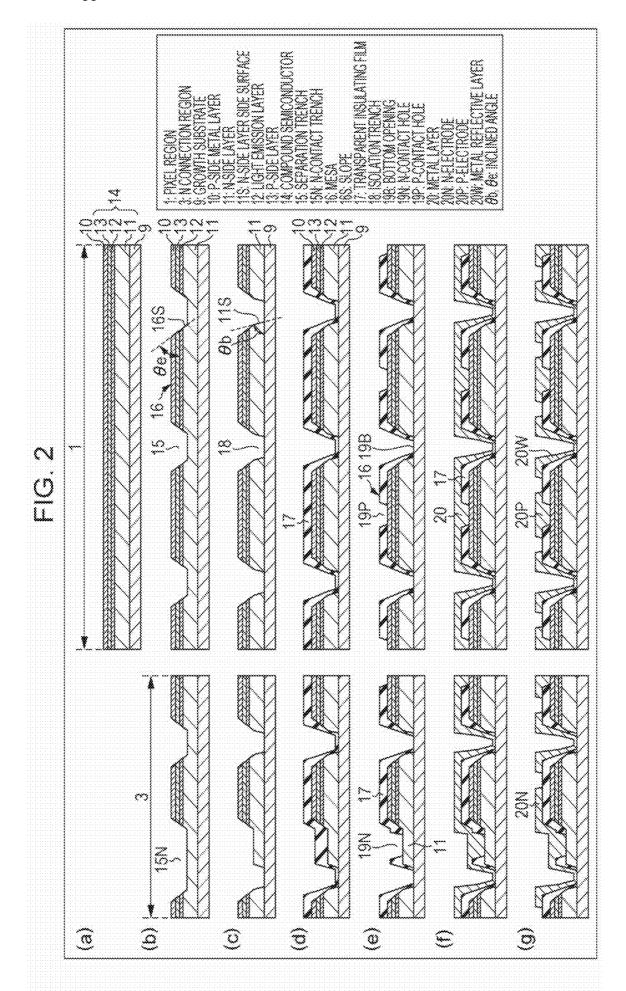

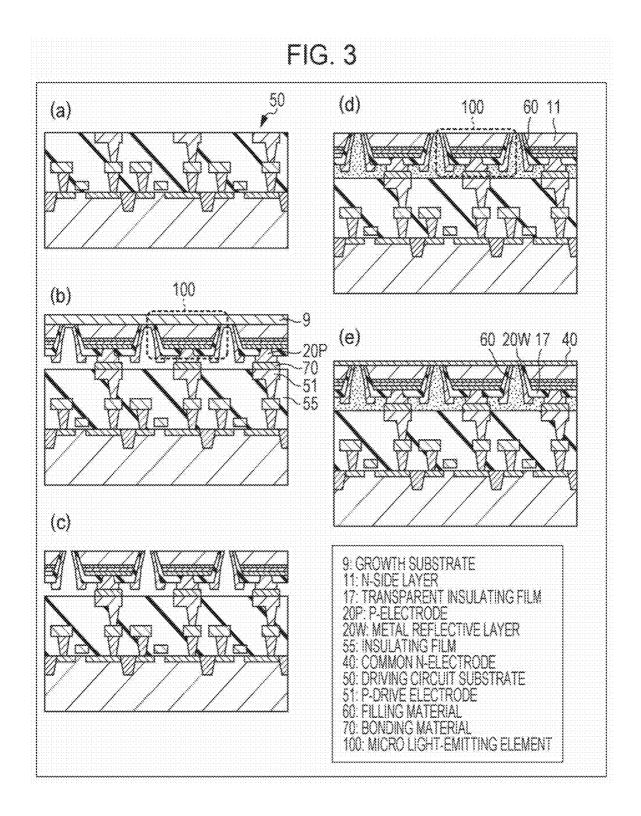

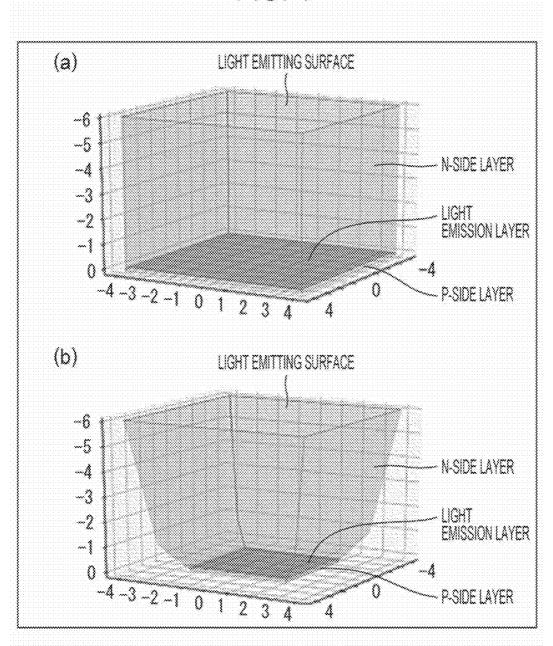

[0037] FIGS. 3(a) to 3(e) are schematic sectional views illustrating a manufacturing flow of the image display element according to Embodiment 1 of the present invention. [0038] FIG. 4(a) is an aerial view of the micro light emitting element having a rectangular parallelepiped structure, and FIG. 4(b) is an aerial view of the micro light emitting element 100 having a truncated bent pyramid type structure according to Embodiment 1 of the present invention

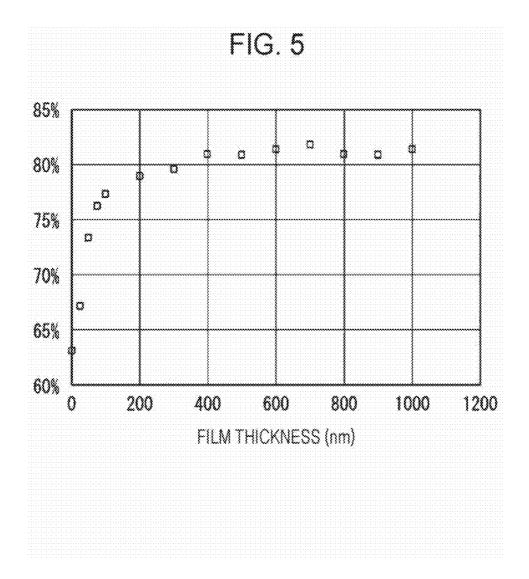

[0039] FIG. 5 is a diagram illustrating a simulation result of film thickness dependency of a transparent insulating film in light extraction efficiency.

[0040] FIGS. 6(a) to 6(e) are diagrams illustrating simulation results of dependency of the light extraction efficiency on dimensions and angles of each unit in the image display element illustrated in FIG. 1(a).

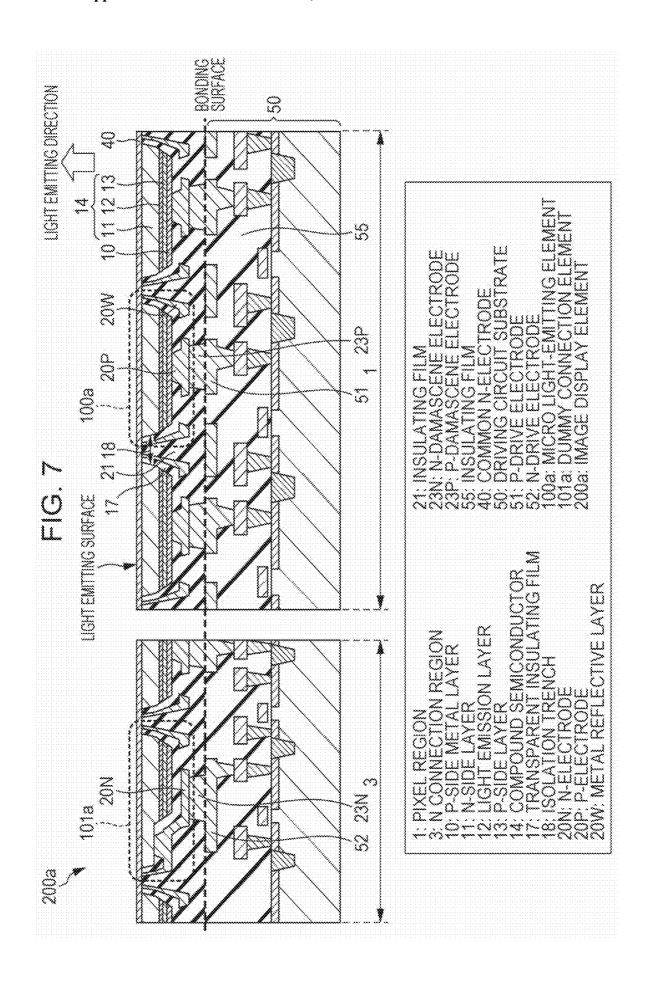

[0041] FIG. 7 is a schematic sectional view of an image display element according to Embodiment 2 of the present invention.

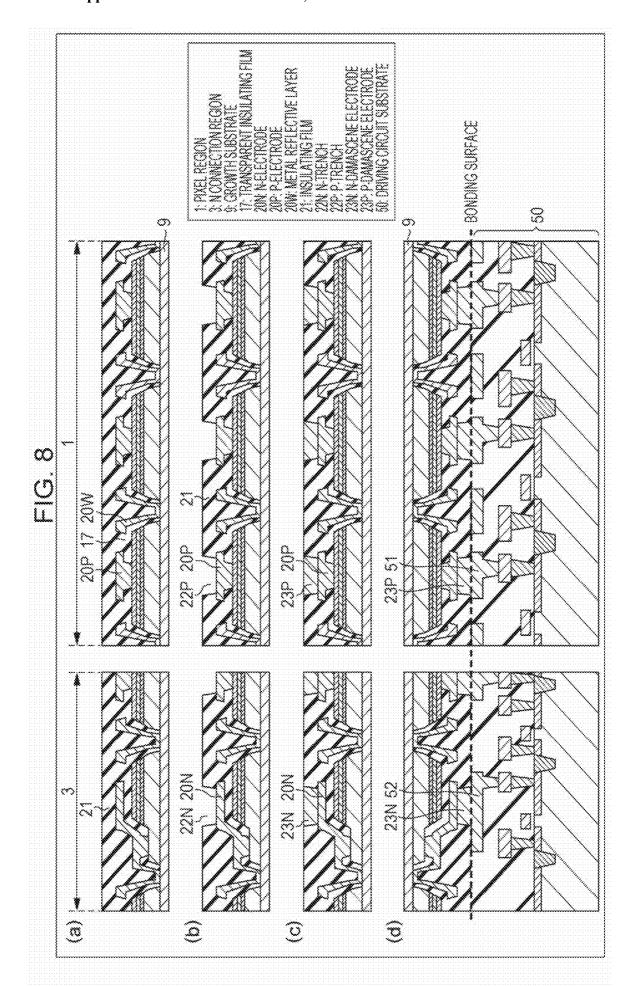

[0042] FIGS. 8(a) to 8(d) are schematic sectional views illustrating a manufacturing flow of the image display element according to Embodiment 2 of the present invention. [0043] FIG. 9(a) is a schematic sectional view of an image display element according to Embodiment 3 of the present invention, and FIG. 9(b) is a schematic plan view of a micro light emitting element according to Embodiment 3 of the present invention.

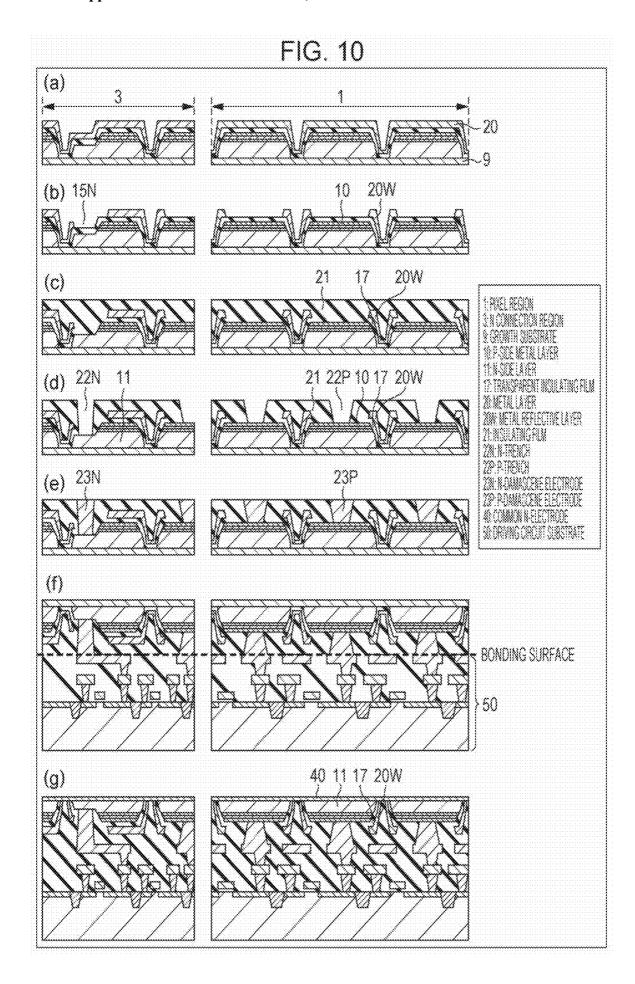

[0044] FIGS. 10(a) to 10(g) are schematic sectional views illustrating a manufacturing flow of the image display element according to Embodiment 3 of the present invention.

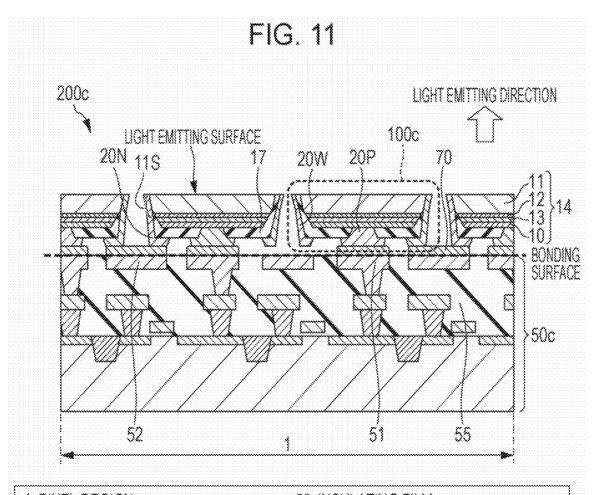

[0045] FIG. 11 is a schematic sectional view of an image display element according to Embodiment 4 of the present invention.

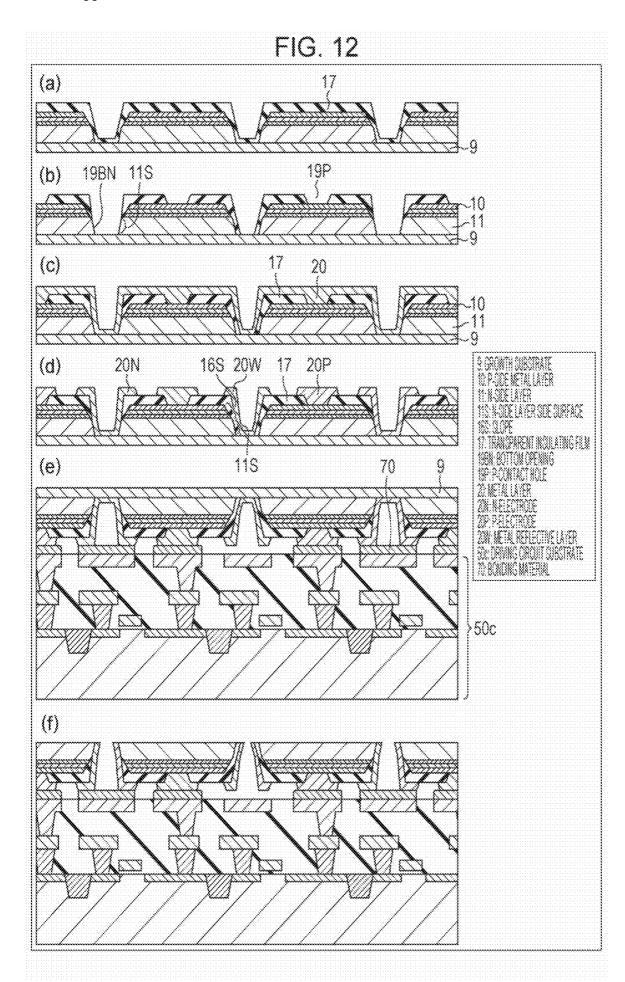

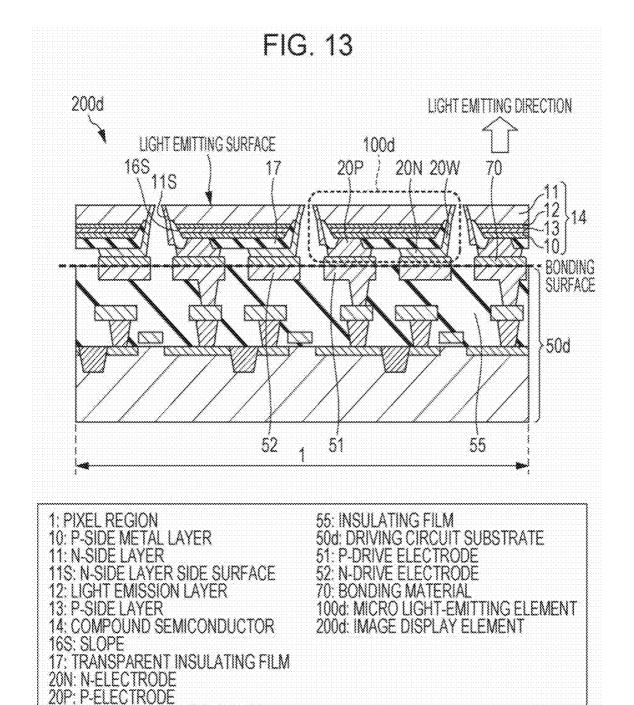

[0046] FIGS. 12(a) to 12(f) are schematic sectional views illustrating a manufacturing flow of the image display element according to Embodiment 4 of the present invention. [0047] FIG. 13 is a schematic sectional view of an image display element according to Embodiment 5 of the present invention.

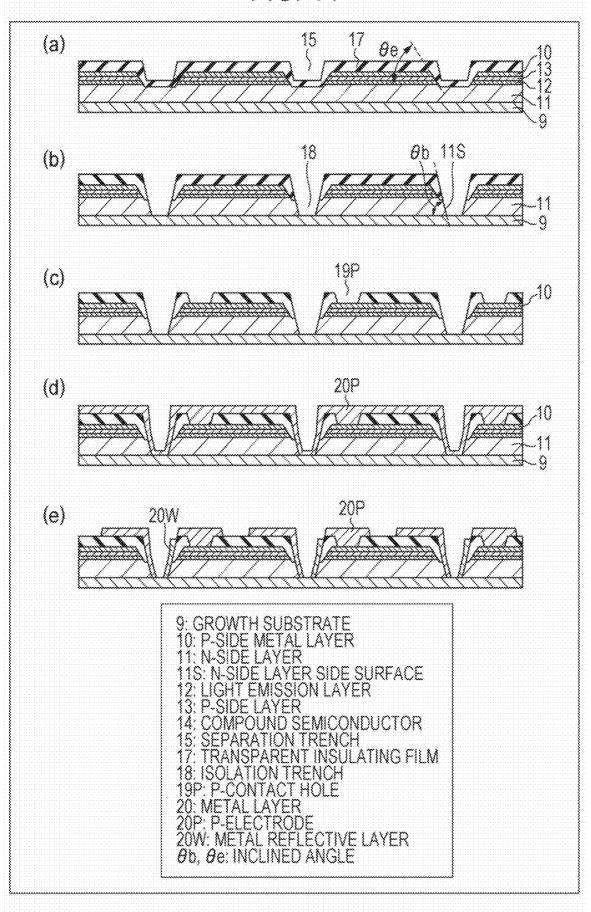

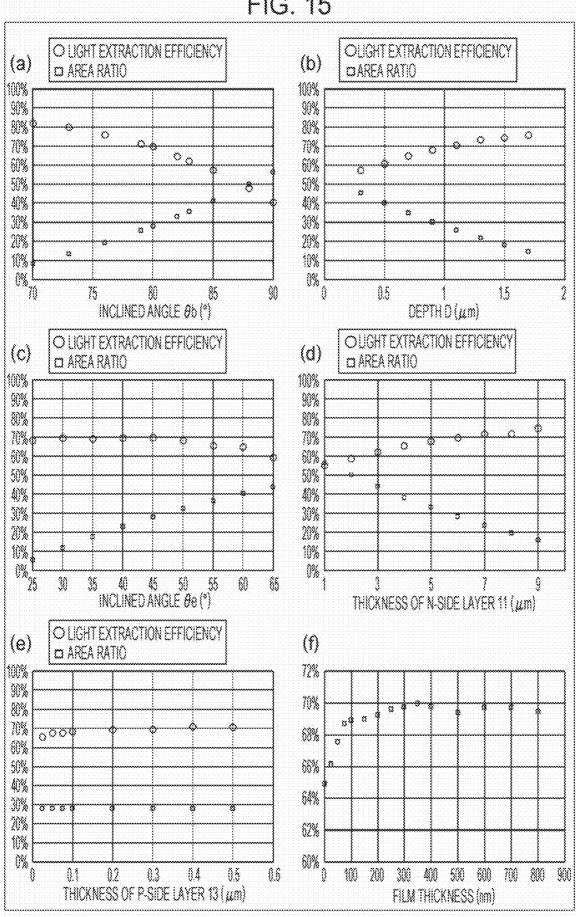

[0048] FIGS. 14(a) to 14(e) are schematic sectional views illustrating a manufacturing flow of the image display element according to Embodiment 5 of the present invention. [0049] FIG. 15(a) to 15(f) are diagrams illustrating simulation results of dependency of the light extraction efficiency on the dimensions and the angles of each unit in the image display element illustrated in FIG. 13.

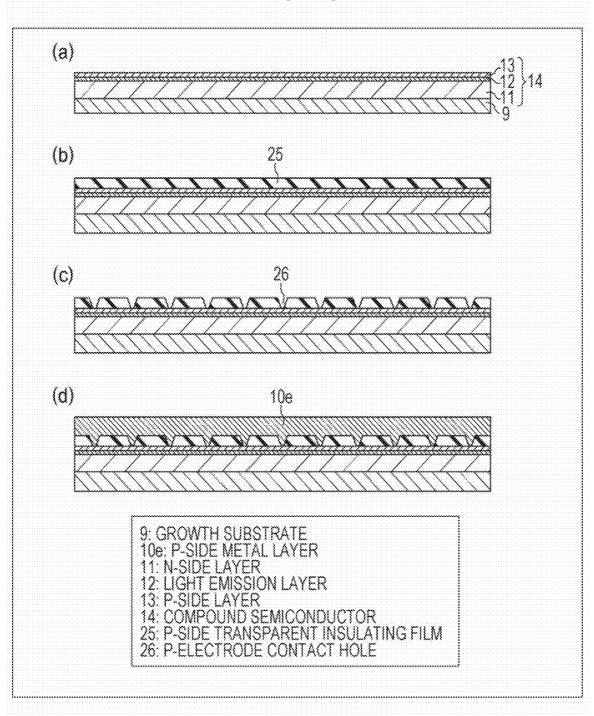

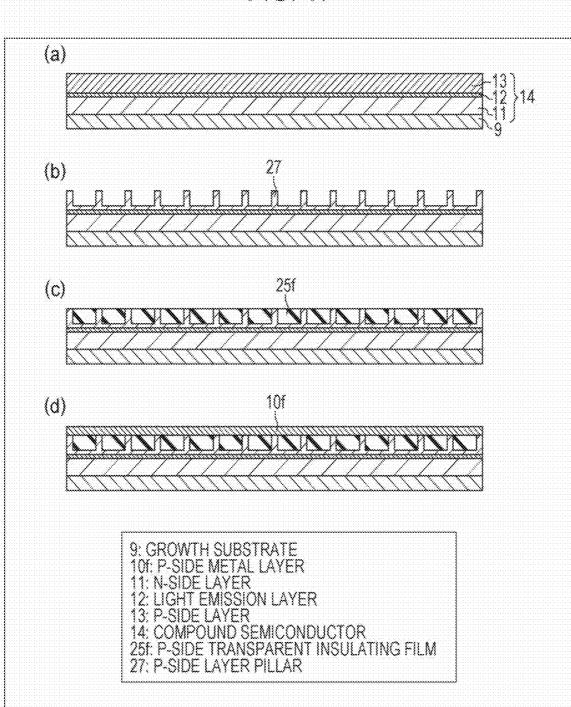

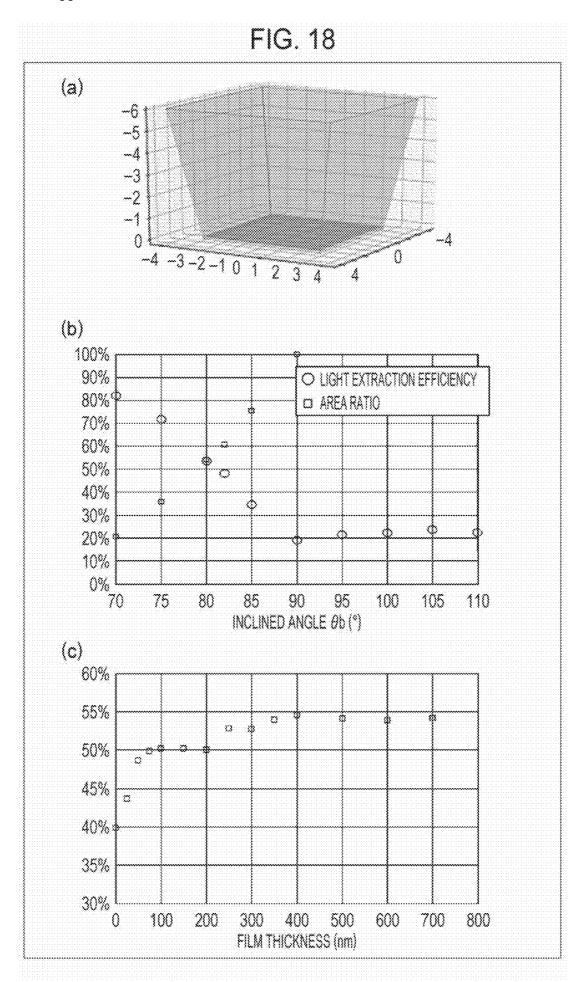

[0050] FIGS. 16(a) to 16(d) are schematic sectional views illustrating a manufacturing flow of an image display element according to Embodiment 6 of the present invention. [0051] FIGS. 17(a) to 17(d) are schematic sectional views illustrating a manufacturing flow of an image display element according to Embodiment 7 of the present invention. [0052] FIG. 18(a) is an aerial view of a micro light emitting element having a truncated pyramid type structure according to Embodiment 8 of the present invention, FIG.

18(b) is a diagram illustrating a simulation result of dependency of the light extraction efficiency on an inclined angle, and FIG. 18(c) is a diagram illustrating a simulation result of the film thickness dependency of a transparent insulating film in the light extraction efficiency.

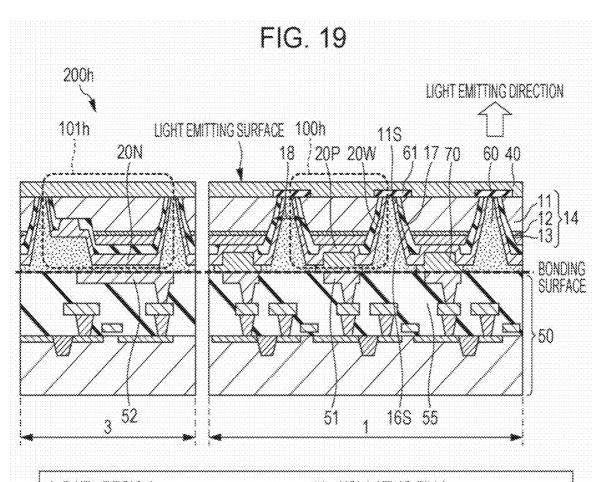

[0053] FIG. 19 is a schematic sectional view of an image display element according to Embodiment 9 of the present invention.

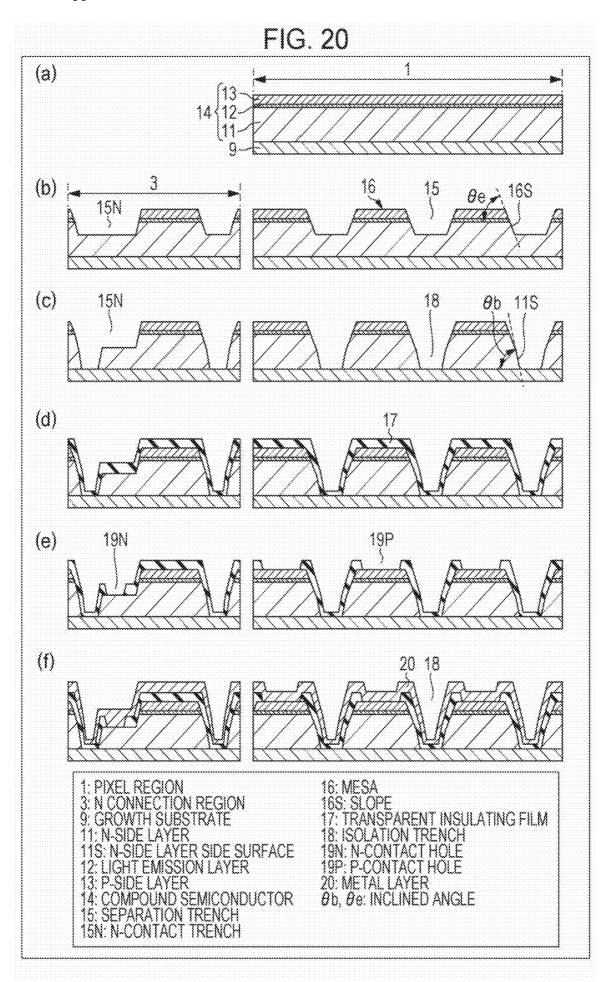

[0054] FIGS. 20(a) to 20(f) are schematic sectional views illustrating a manufacturing flow of a micro light emitting element according to Embodiment 9 of the present invention.

[0055] FIGS. 21(a) to 21(c) are schematic sectional views illustrating a manufacturing flow of the image display element according to Embodiment 9 of the present invention. [0056] FIGS. 22(a) to 22(f) are schematic sectional views illustrating a manufacturing flow of a micro light emitting element according to Embodiment 10 of the present invention

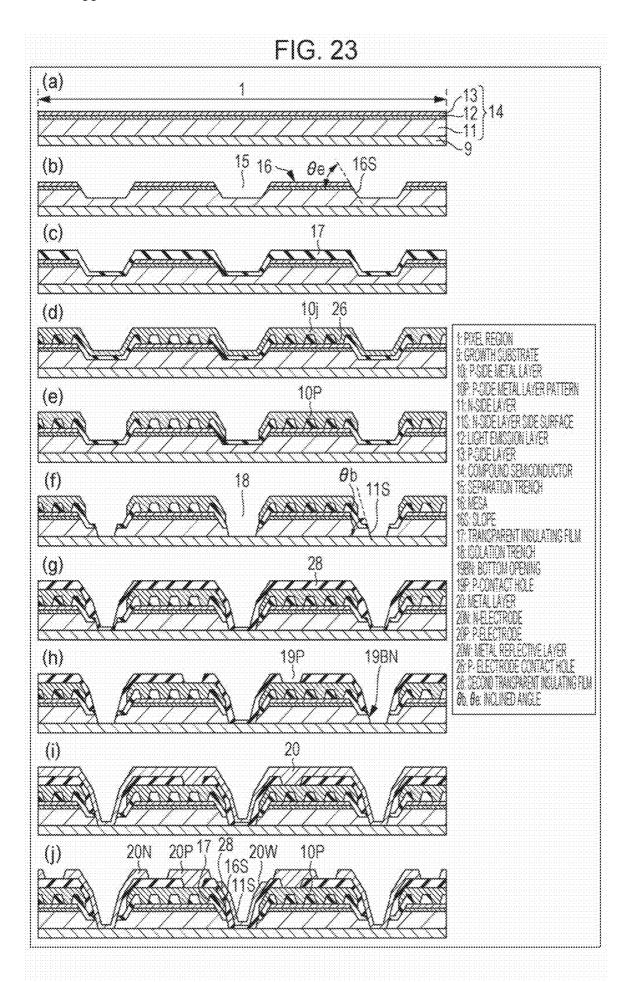

[0057] FIGS. 23(a) to 23(j) are schematic sectional views illustrating a manufacturing flow of a micro light emitting element according to Embodiment 11 of the present invention.

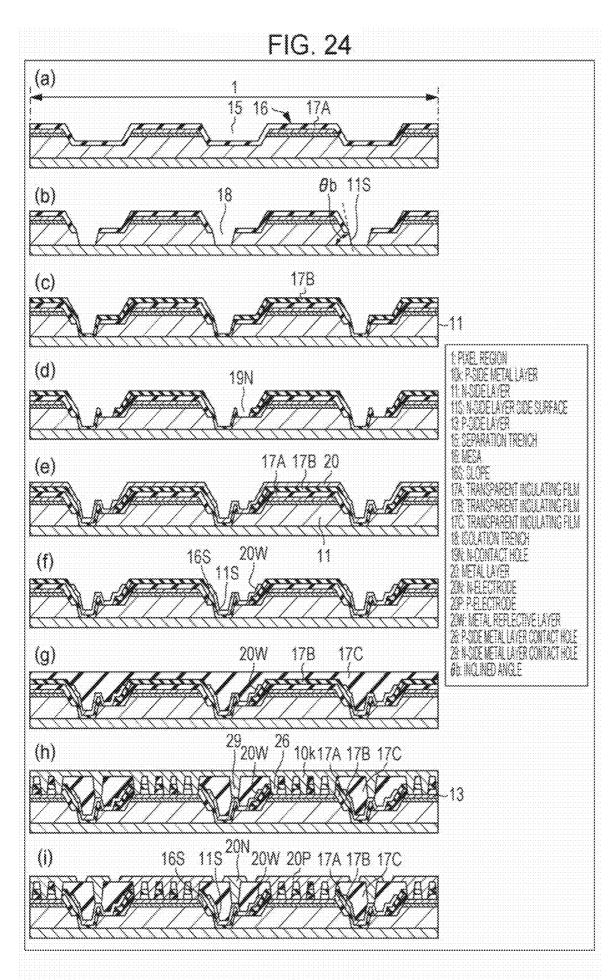

[0058] FIGS. 24(a) to 24(i) are schematic sectional views illustrating a manufacturing flow of a micro light emitting element according to Embodiment 12 of the present invention.

#### DESCRIPTION OF EMBODIMENTS

#### Embodiment 1

[0059] (Configuration of Image Display Element 200)

[0060] FIG.  $\mathbf{1}(a)$  is a schematic sectional view of an image display element  $\mathbf{200}$  according to Embodiment 1 of the present invention. FIG.  $\mathbf{1}(b)$  is a schematic sectional view of a micro light emitting element  $\mathbf{100}$  according to Embodiment 1 of the present invention. FIG.  $\mathbf{1}(c)$  is a schematic plan view of the micro light emitting element  $\mathbf{100}$  according to Embodiment 1 of the present invention. The image display element  $\mathbf{200}$  including a plurality of micro light emitting elements  $\mathbf{100}$  will be described below, as an example, with reference to FIGS.  $\mathbf{1}$  to  $\mathbf{6}$ . In descriptions of the configuration of the image display element  $\mathbf{200}$ , a light emitting surface is referred to as an upper surface, a surface on an opposite side of the light emitting surface side is referred to as a lower surface, and surfaces on sides other than the upper surface and the lower surface are referred to as side surfaces.

[0061] As illustrated in FIG. 1(a), the image display element 200 includes the plurality of micro light emitting elements 100 and a driving circuit substrate 50. The driving circuit substrate 50 supplies a current to the micro light emitting element 100 in a pixel region 1 to control light emission. The pixel region 1 is a region in which the micro light emitting elements 100 are arranged on the driving circuit substrate 50 in a two-dimensional array shape. The image display element 200 has the pixel region 1.

[0062] The micro light emitting element 100 emits light to the opposite side of the driving circuit substrate 50. A wavelength conversion layer, a light diffusion layer, a color filter, a micro-lens, and the like may be arranged on the light emitting surface side in the micro light emitting element 100. These components are not directly related to one form of the present invention, and thus are not illustrated in the drawings.

[0063] The driving circuit substrate 50 is configured by a micro light emitting element driving circuit, a row selection circuit, a column signal output circuit, an image processing circuit, an input and output circuit, and the like. The micro light emitting element driving circuit controls a current to be supplied to each micro light emitting element 100. The row selection circuit selects each row of the micro light emitting elements 100 arranged in a two-dimensional matrix shape. The column signal output circuit outputs a light emitting signal to each column. The image processing circuit calculates the light emitting signal based on an input signal.

[0064] A P-drive electrode (first driving electrode) 51 connected to the micro light emitting element 100 and an N-drive electrode (second driving electrode) 52 are disposed on a surface of the driving circuit substrate 50 on a bonding surface side. That is, the surface of the driving circuit substrate 50 faces a surface of the micro light emitting element 100 on an opposite side of the light emitting surface side. In FIG. 1, the driving circuit substrate 50 is a silicon substrate (semiconductor substrate) in which an LSI is formed, but other form of the driving circuit substrate such as glass substrate with TFT circuit is also possible. Since the driving circuit substrate can be manufactured by a well-known technology, detailed descriptions of the function and the configuration thereof will not be made.

[0065] P-drive electrodes 51 for supplying a current to the micro light emitting elements 100 are arranged on the surface of the pixel region 1 in the driving circuit substrate 50 in a two-dimensional array shape. Alternatively, the N-drive electrode 52 is disposed on the surface (surface of an N connection region 3) of the driving circuit substrate 50 on the outside of the pixel region 1. The N-drive electrode 52 is electrically connected to a common N-electrode (light emitting surface-side electrode) 40 through a metal reflective layer 20W.

[0066] Various planar shapes such as a rectangle, a polygon, a circle, and an ellipse may be provided as the shape of the micro light emitting element 100. The longest length of the micro light emitting element 100 in a longitudinal direction of the upper surface is equal to or less than  $60 \, \mu m$ . Regarding the image display element 200, 3000 or more micro light emitting elements 100 are integrated in the pixel region 1.

[0067] The micro light emitting element 100 includes a compound semiconductor 14. Generally, the compound semiconductor 14 is configured in a manner that an N-side layer (first conductive layer) 11, a light emission layer 12, and a P-side layer (second conductive layer) 13 are stacked in order from the light emitting surface side. The P-side layer 13 has a conductivity type opposite to the conductivity type of the N-side layer 11.

[0068] For example, in a case where the micro light emitting element 100 emits light in a wavelength band from ultraviolet light to a green color, the compound semiconductor 14 is a semiconductor of a nitride semiconductor (AlInGaN series). In a case where the micro light emitting element 100 emits light in a wavelength band from a yellow color to a red color, the compound semiconductor 14 is an AlInGaP-based semiconductor. Alternatively, in a case where the micro light emitting element 100 emits light in a wavelength band from the red color to infrared light, the compound semiconductor 14 is an AlGaAs-based or GaAs-based semiconductor. Depending on wavelength, other

material such as quantum dot of CdSe or InP and Perovskite nanocrystal can be used as the compound semiconductor 14. [0069] The configuration of the compound semiconductor 14, in which the N-side layer 11 is disposed on the light emitting surface side will be described below. However, a configuration in which the P-side layer 13 is disposed on the light emitting surface side may be made. Normally, each of the N-side layer 11, the light emission layer 12, and the P-side layer 13 is optimized by including a plurality of layers instead of a single layer. However, this is not directly related to the form of the present invention, and thus detailed descriptions of the detailed structure of each of the N-side layer 11, the light emission layer 12, and the P-side layer 13 are not made.

[0070] Normally, the light emission layer 12 is interposed between an N-type layer and a P-type layer. However, a case where the N-type layer and the P-type layer include a non-doped layer or a layer having dopants of opposite conductivity may be provided. For this reason, the N-type layer and the P-type layer will be described below as an N-side layer and a P-side layer, respectively.

[0071] The surface of the driving circuit substrate 50 is a bonding surface bonded to the plurality of micro light emitting elements 100, and the plurality of micro light emitting elements 100 are stuck to the surface. In the embodiment, the micro light emitting element 100 is a so-called vertical type. The micro light emitting element 100 includes a P-electrode (first electrode) 20P on the lower surface and includes a common N-electrode 40 on the upper surface.

[0072] Specifically, in the micro light emitting element 100, the common N-electrode 40 is disposed on the light emitting surface side, and the P-electrode 20P is disposed on the surface on an opposite side of the light emitting surface side. The light emitting surface of the micro light emitting element 100 is the upper surface of the micro light emitting element 100. The side opposite to the light emitting surface is a lower side of the micro light emitting element 100, on which the P-electrode 20P is disposed. The P-electrode 20P and the P-drive electrode 51 are connected in a one-to-one relation.

[0073] In the pixel region 1, the P-electrode 20P connected to the P-side layer 13 is disposed on the lower surface of the micro light emitting element 100. The P-electrode 20P is connected to the P-drive electrode 51 on the driving circuit substrate 50 through a bonding material 70, and thus transmits a current supplied from the driving circuit substrate 50 to the P-side layer 13.

[0074] The current passing through the P-side layer 13 further passes through the light emission layer 12 and the N-side layer 11 to flow to the common N-electrode 40. The current flows to the N-drive electrode 52 of the driving circuit substrate 50 in the N connection region 3 on the outside of the pixel region 1. In this manner, the micro light emitting element 100 emits light at predetermined intensity, in accordance with the current amount supplied by the driving circuit substrate 50.

[0075] Alternatively, in FIG. 1, in order to connect the common N-electrode 40 and the N-drive electrode 52 by the same structure as the structure of connecting the P-electrode 20P and the P-drive electrode 51, a dummy connection element 101 configured with the same material as the material of the micro light emitting element 100 is used. With such a configuration, it is possible to simplify a

connection process between the micro light emitting element 100 and the driving circuit substrate 50. A connection method between the common N-electrode 40 and the N-drive electrode 52 may be different from a connection method between the P-electrode 20P and the P-drive electrode 51. Alternatively, the dummy connection element 101 may be processed to be a rod extending in a depth direction of the paper surface in FIG. 1(a) or 1(b).

[0076] The lower surface of the P-side layer 13 is in contact with a P-side metal layer (first metal film) 10. The P-side metal layer 10 has a need to reflect light reaching the lower surface of the P-side layer 13 upward with high efficiency, and thus preferably covers most of the lower surface of the P-side layer 13. The P-side metal layer 10 prevents downward emission of light. The P-side metal layer 10 is disposed on a surface on the opposite side of the light emitting surface side and is electrically connected to the P-electrode 20P and the P-side layer 13. The P-side metal layer 10 covers the P-side layer 13 from the surface on the opposite side of the light emitting surface side.

[0077] The P-side metal layer 10 may be configured by a single layer or a plurality of layers. Preferably, a metal layer having high reflectivity for visible light is disposed on a side of the P-side metal layer 10, which is in contact with the P-side layer 13. For example, the P-side metal layer 10 includes a metal layer M1 containing silver or aluminum as the main component, on the P-side layer 13 side. In order to realize a favorable ohmic contact between the metal layer M1 and the P-side layer 13, metal such as palladium or nickel may be partially arranged, or a very thin metal film of palladium, nickel, or the like may be disposed.

[0078] The common N-electrode 40 is formed from a transparent conductive layer, that is, a transparent conductive film electrically connected to the N-side layer 11. The common N-electrode 40 may be an oxide semiconductor such as indium tin oxide (ITO) and indium zinc oxide (IZO) or may be a silver nanofiber layer.

[0079] Alternatively, the common N-electrode 40 may be a mesh-like metal thin film disposed at the upper portion of a filling material 60. The micro light emitting element 100 includes the common N-electrode 40 on the surface of the N-side layer 11 on the light emitting surface side. An isolation trench 18 formed between the plurality of micro light emitting elements 100 is filled with the filling material 60.

[0080] The micro light emitting elements 100 are separately divided by the isolation trench 18. For this reason, it is possible to prevent light leakage between the micro light emitting elements 100 adjacent to each other. The entire periphery of the side surface of the light emission layer 12 constitutes a portion of a slope 16S. That is, the slope 16S is formed around the light emission layer 12. The slope 16S constitutes a portion of the side surface of the N-side layer 11, the entire periphery of the side surface of the light emission layer 12, and the entire periphery of a portion of the side surface of the P-side layer 13. As illustrated in FIG.  $\mathbf{1}(c)$ , in a case where a planar shape of the micro light emitting element 100 is rectangular, a portion of the periphery of the side surface of one micro light emitting element 100 constitutes four slopes 16S. Preferably, all the side surfaces of the P-side layer 13 are inclined similar to the light emission layer 12. However, the lower surface of the P-side layer 13 may be bent from the slop 16S depending on a manufacturing flow.

[0081] In the embodiment, a case where the planar shape of the micro light emitting element 100 is rectangular will be described. However, in a case where the planar shape of the micro light emitting element 100 is polygonal, a plurality of slopes 16S are formed. Specifically, in a case where N corners (N is a natural number) of a polygon being the planar shape of the micro light emitting element 100 are provided, N pieces of slopes 16S are formed.

[0082] Alternatively, in a case where the planar shape of the micro light emitting element 100 is circular, the slope 16S is formed by a truncated conical side surface. An inclined angle (second inclined angle)  $\theta$ e of the slope 16S is approximately 40° to 55°, and preferably 35° to 60° in consideration of manufacturing variations. The inclined angle  $\theta$ e is an angle formed by the slope 16S and a horizontal surface (upper surface) S1 of the light emission layer 12.

[0083] As illustrated in FIG. 1(b), the slope 16S extends from the side surface of the P-side layer 13 to a portion of the side surface of the N-side layer 11. However, the slope 16S does not reach the light emitting surface, that is, the upper surface of the micro light emitting element 100. The portion of the side surface of the N-side layer 11 constitutes an N-side layer side surface (first conductive layer side surface) 11S. The N-side layer side surface 11S extends from the slope 16S to the light emitting surface.

[0084] The inclined angle (first inclined angle)  $\theta b$  of the N-side layer side surface 11S is an angle larger than the inclined angle  $\theta e$ . The inclined angle  $\theta b$  is less than 90°, and preferably small.

[0085] In a case where the horizontal surface S1 of the light emission layer 12 is parallel to the horizontal surface (upper surface) S2 of the N-side layer 11, the inclined angle  $\theta$ b is an angle formed by the N-side layer side surface 11S and the horizontal surface S2 of the N-side layer 11. In a case where the horizontal surface S1 of the light emission layer 12 is not parallel to the horizontal surface S2 of the N-side layer 11, the inclined angle  $\theta$ b is an angle formed by the N-side layer side surface 11S and the horizontal surface S2 of the N-side layer 11.

[0086] However, in a case where the size of the micro light emitting element 100 is small (for example, in a case where the long side of the upper surface of the micro light emitting element 100 is equal to or less than  $10~\mu m$ ), if the inclined angle  $\theta b$  is reduced, the area of the horizontal surface of the light emission layer 12 is reduced. If the area of the horizontal surface of the light emission layer 12 is reduced, current density of a current passing through the light emission layer 12 may increase, and thus internal quantum efficiency may decrease. Thus, the inclined angle  $\theta b$  is preferably about 700 to 850.

[0087] The slope 16S and the N-side layer side surface 11S are covered by a transparent insulating film (first transparent insulating film) 17. The transparent insulating film 17 is covered by a metal reflective layer (second metal film) 20W. That is, the slope 16S and the N-side layer side surface 11S are covered together by the metal reflective layer 20W. The transparent insulating film 17 is transparent to visible light as with  $\mathrm{SiO}_2$ , and a material having a refractive index which is less than the refractive index of the compound semiconductor 14 is preferable.

[0088] The transparent insulating film 17 is disposed between the slope 16S and the metal reflective layer 20W. The transparent insulating film 17 extends between the

N-side layer side surface 11S and the metal reflective layer 20W. Here, a portion of the transparent insulating film 17, which is disposed between the slope 16S and the metal reflective layer 20W is referred to as a first transparent insulating film. A portion thereof, which is disposed between the N-side layer side surface 11S and the metal reflective layer 20W is referred to as a second transparent insulating film. In this case, the second transparent insulating film is set to be obtained by the first transparent insulating film extending between the N-side layer side surface 11S and the metal reflective layer 20W. That is, the first transparent insulating film and the second transparent insulating film are integrally formed. The film thickness of the transparent insulating film 17 is preferably equal to or more than 75 nm, and more preferably equal to or more than 400 nm, in particular.

[0089] The metal reflective layer 20W may be configured by a single layer or a plurality of layers. Preferably, the metal reflective layer 20W includes a metal layer M2 on the transparent insulating film 17 side, that is, on the compound semiconductor 14 side. The metal layer M2 contains silver or aluminum having high reflectivity for visible light, as the main component. The metal reflective layer 20W has a need to shield light, and thus the entire thickness thereof is preferably several tens or more of nm. The same material is used for the P-electrode 20P and the metal reflective layer 20W in order to simplify a manufacturing flow. However, different materials may be used.

[0090] In plan view from a side opposite to the light emitting surface side, the metal reflective layer 20W is preferably disposed to overlap the P-side metal layer 10. In plan view from a side opposite to the light emitting surface, if a space is provided between the metal reflective layer 20W and the P-side metal layer 10, light is emitted from the space to the outside, and this causes optical crosstalk. Thus, preferably, there is no space. The filling material 60 may be a transparent material.

[0091] Since a situation in which light is emitted from the micro light emitting element 100 in a bottom surface direction and a side surface direction does not occur by the metal reflective layer 20W and the P-side metal layer 10, it is possible to prevent the occurrence of optical crosstalk even though the filling material 60 is transparent resin. In a micro light emitting element in the related art, the occurrence of optical crosstalk is prevented by the filling material, but it is difficult to completely prevent the occurrence of optical crosstalk by bubbles appeared in the filling material.

[0092] Alternatively, in the micro light emitting element in the related art, it is necessary to use a special material such as a light absorbing material like carbon black or a white resin containing  ${\rm TiO}_2$  particles, as the filling material. Thus, it is necessary to increase a filling time for preventing generation of bubbles in the filling material. For this reason, the filling material is expensive, and thus manufacturing cost increases.

[0093] However, in the form of the present invention, it is easy to perform material selection of the filling material 60 and to product the filling material 60. Thus, it is possible to decrease manufacturing cost in comparison to a case of manufacturing the micro light emitting element in the related art

[0094] (Manufacturing Flow of Micro Light Emitting Element 100)

[0095] Next, the manufacturing flow of the micro light emitting element 100 will be described with reference to

FIGS. 2(a) to 2(g). FIGS. 2(a) to 2(g) are schematic sectional views illustrating the manufacturing flow of the micro light emitting element 100 according to Embodiment 1 of the present invention. In descriptions of the manufacturing flow of the micro light emitting element 100, the P-side metal layer 10 side is set to be upper, and a growth substrate 9 side is set to be lower.

[0096] A sectional view of the pixel region 1 is illustrated on the right side in FIGS. 2(a) to 2(g), and a sectional view of the N connection region 3 is illustrated on the left side in FIGS. 2(a) to 2(g). As illustrated in FIG. 2(a), the compound semiconductor 14 is formed by sequentially stacking the N-side layer 11, the light emission layer 12, and the P-side layer 13 on the growth substrate 9. The P-side metal layer 10 is further deposited on the compound semiconductor 14.

[0097] After the P-side metal layer 10 is deposited on the compound semiconductor 14, as illustrated in FIG. 2(b), a separation trench 15 is formed by etching portions of the P-side metal layer 10, the P-side layer 13, the light emission layer 12, and the N-side layer 11. At this time, a portion including the light emission layer 12 serves as a mesa 16. The mesa 16 is configured by the N-side layer 11, the light emission layer 12, the P-side layer 13, and the P-side metal layer 10. As illustrated in FIG. 1(c), when viewed from the upper surface, the separation trench 15 is formed at equal intervals in an up-down and a right-left direction. The shape of the mesa 16 is a shape of a truncated pyramid.

[0098] The shape of the mesa 16 is not limited to a truncated pyramid and may be a truncated cone or another truncated polygon. In the pixel region 1, the separation trench 15 separates the micro light emitting elements 100 from each other. And, in the N connection region 3, an N-contact trench 15N is formed simultaneous with the separation. An N-contact hole 19N is formed later in the N-contact trench 15N.

[0099] The slope 16S as the side surface of the mesa 16 is formed and processed such that the inclined angle  $\theta e$  as the angle formed by the slope 16S and the horizontal surface of the light emission layer 12 is, for example, 500. Preferably, the slope 16S is formed such that the inclined angle  $\theta e$  is 40° to 55°. The slope 16S reflects light traveling in a direction parallel to the horizontal surface of the light emission layer 12, which occupies a large part of light emitted from the light emission layer 12, toward the light emitting surface. Thus, it is possible to increase light extraction efficiency of the micro light emitting element 100.

[0100] In a case where the slope 16S is perpendicular to the horizontal surface of the light emission layer 12, light emitted in the direction parallel to the horizontal surface of the light emission layer 12 repeats reflection, and thereby is not emitted to the outside. If the inclined angle  $\theta$ e deviates from 450 largely, an incident angle of light, which is emitted from the light emission layer 12 and is incident to the light emitting surface, becomes too large, when the light is emitted from the light emission layer 12 and reflected by the slope 16S. Thus, total reflection occurs on the light emitting surface, and the light is not emitted to the outside. The inclined angle  $\theta$ e may be different for each of the plurality of side surfaces of the mesa 16. In this case, a plurality of inclined angles  $\theta e$  is provided. The minimum angle of the plurality of inclined angles  $\theta e$  is preferably 400 to 550, and further preferably, all the inclined angles  $\theta e$  are  $40^{\circ}$  to  $55^{\circ}$ . [0101] After the separation trench 15 is formed, as illustrated in FIG. 2(c), an isolation trench 18 that divides the

compound semiconductor 14 of the micro light emitting element 100 is formed. The side surface of the N-side layer 11, which is formed by the isolation trench 18 is the N-side layer side surface 11S. The N-side layer side surface is processed and formed such that the inclined angle  $\theta$ b as an angle formed by the N-side layer side surface 11S and the horizontal surface of the growth substrate 9 is, for example,  $80^{\circ}$ . Preferably, the N-side layer side surface 11S is formed such that the inclined angle  $\theta$ b is 700 to 850. That is, the inclined angle  $\theta$ b is preferably larger than the inclined angle  $\theta$ e

[0102] In order to improve light extraction efficiency of the micro light emitting element 100, preferably, the inclined angle  $\theta b$  is as small as possible in an angle range of being larger than the inclined angle  $\theta c$ . In the subsequent process, the growth substrate 9 is separated, and thus an interface between the N-side layer 11 and the growth substrate 9 or the processed surface of the N-side layer 11 serves as the light emitting surface. Thus, the inclined angle  $\theta c$  is equal to an angle formed by the N-side layer side surface 11S and the light emitting surface.

[0103] In FIG. 2(c), the isolation trench 18 reaches the growth substrate 9, but the N-side layer 11 having a predetermined thickness may remain. That is, the isolation trench 18 may not reach the growth substrate 9. In FIG. 3(c) as the subsequent process, after the growth substrate 9 is separated, the remaining N-side layer 11 is removed by etching, polishing, and the like. Thus, as illustrated in FIG. 1(a), it is possible to individually separate the micro light emitting elements 100 from each other.

[0104] The shape of the micro light emitting element 100 is important in a state where the image display element 200 is formed. Temporary shape of the micro light emitting element in the middle of the manufacturing flow is not important. The inclined angle  $\theta b$  of the N-side layer side surface 11S may be different for each of a plurality of side surfaces of the N-side layer 11. In this case, a plurality of inclined angles  $\theta b$  is provided. The minimum angle of the plurality of inclined angles  $\theta b$  is preferably 700 to 850, and further preferably, all the inclined angle  $\theta b$  are 700 to 850.

[0105] After the isolation trench 18 is formed, as illustrated in FIG. 2(d), the transparent insulating film 17 is deposited to cover the exposed portions of the growth substrate 9, the N-side layer 11, the light emission layer 12, the P-side layer 13, and the P-side metal layer 10. Here, a  $SiO_2$  film having a thickness of 400 nm is deposited as the transparent insulating film 17 by a CVD method. Films of SiN, SiON, and SiCO or a film obtained by stacking the above films may be provided as the transparent insulating film 17 in place of the  $SiO_2$  film. Preferably, the transparent insulating film 17 is formed by the CVD method such that the thickness of the transparent insulating film 17 that covers the side surface of the micro light emitting element 100 is uniform.

[0106] After the transparent insulating film 17 is deposed, as illustrated in FIG. 2(e), a P-contact hole 19P is formed in the mesa 16 of the pixel region 1, and an N-contact hole 19N is formed in the N-contact trench 15N of the N connection region 3. Specifically, the N-contact hole 19N is formed by removing the transparent insulating film 17 on the N-side layer 11 in the N-contact trench 15N. At this time, a bottom opening 19B may be formed in the transparent insulating film 17 deposited on the bottom of the isolation trench 18.

The P-contact hole 19P reaches the P-side metal layer 10, and the N-contact hole 19N reaches the N-side layer 11 of the N-contact trench 15N.

[0107] Further, as illustrated in FIG. 2(f), the metal layer 20 is deposited on the transparent insulating film 17. Then, as illustrated in FIG. 2(g), the metal layer 20 is patterned. Thus, the metal layer 20 is processed to serve as the P-electrode 20P on the P-contact hole 19P, to serve as the metal reflective layer 20W in the periphery of the isolation trench 18, and to serve as the N-electrode (second electrode) 20N in the N connection region 3.

[0108] As described above, the micro light emitting element 100 is formed by a very simple manufacturing flow in which a process of depositing the transparent insulating film 17 is performed once, a process of forming the metal layer 20 is performed twice, and a photolithographic process is performed four times. Further, the dummy connection element 101 is formed in the N connection region 3, and thus a connection with the driving circuit substrate 50 becomes simple as described later.

[0109] (Manufacturing Flow of Image Display Element 200)

[0110] Next, the manufacturing flow of the image display element 200 will be described using FIG. 3. FIGS. 3(a) to 3(e) are schematic sectional views illustrating the manufacturing flow of the image display element 200 according to Embodiment 1 of the present invention. In descriptions of the manufacturing flow of the image display element 200, the growth substrate 9 side is set to be upper, and the driving circuit substrate 50 side is set to be lower.

[0111] As illustrated in FIG. 3(a), firstly, the driving circuit substrate 50 is manufactured. The driving circuit substrate 50 is formed on, for example, a single crystal silicon substrate (wafer) by a general CMOS process. Here, each of the micro light emitting element 100 and the driving circuit substrate 50 may be in a wafer state, and the micro light emitting element 100 may be divided in a unit of the image display element 200. Alternatively, both the micro light emitting element 100 and the driving circuit substrate 50 may be divided in a unit of the image display element 200. [0112] After the driving circuit substrate 50 is manufactured, as illustrated in FIG. 3(b), the micro light emitting element 100 and the dummy connection element 101 are stuck to the driving circuit substrate 50. The bonding material 70 is formed on the P-drive electrode 51 and the N-drive electrode **52** of the driving circuit substrate **50**. The P-drive electrode 51 and the N-drive electrode 52 are physically and electrically connected to the P-electrode 20P and the N-electrode 20N through the bonding material 70, respectively. At this time, the P-electrode 20P and the N-electrode 20N are precisely aligned to overlap the corresponding P-drive electrode 51 and N-drive electrode 52.

[0113] The bonding material 70 is a conductive connection member and is a gold bump, a conductive paste of gold or silver, an anisotropic conductive film (ACF), or nanoparticles of gold, silver, palladium, or the like. The bonding material 70 can be omitted when the P-electrode 20P and the P-drive electrode 51 can be bonded directly. As illustrated in FIG. 3(c), the growth substrate 9 is separated to be removed. Various methods such as grinding, polishing, plasma etching, wet etching, sacrificial layer wet etching, and laser lift-off can be used to remove the growth substrate 9. At this time, processing, for example, removing of a portion of the N-side layer 11 may be performed.

[0114] After the growth substrate 9 is removed, as illustrated in FIG. 3(d), a space between the micro light emitting elements 100 is filled with the filling material 60. Here, for example, transparent silicon resin is used as the filling material 60. Dry etching, wet washing, and the like are performed to expose the N-side layer 11 of the micro light emitting element 100. Then, as illustrated in FIG. 3(e), the common N-electrode 40 is deposited to cover the exposed portions of the N-side layer 11, the transparent insulating film 17, the metal reflective layer 20W, and the filling material 60. Here, for example, an ITO film is used as the common N-electrode 40. With the above-described processes, the image display element 200 is formed.

[0115] (Light Emission Efficiency of Micro Light Emitting Element 100)

[0116] Light emission efficiency of the micro light emitting element 100 formed in a manner as described above was evaluated. Regarding the micro light emitting element 100, the arrangement pitch is 10  $\mu$ m, the shape is a square, the inclined angle  $\theta$ b is 800, the inclined angle  $\theta$ e is 500, the thickness of the P-side layer 13 is 100 nm, and the thickness of the N-side layer 11 is 6 m. In addition, the size of the upper surface of the N-side layer 11 is 8  $\mu$ m×8  $\mu$ m, and the depth D at a portion occupied by the N-side layer 11 in the slope 16S is 1  $\mu$ m.

[0117] The depth D is a depth in the vertical direction (direction from the upper surface of the micro light emitting element 100 toward the lower surface). The compound semiconductor 14 is a nitride semiconductor. The N-side layer 11 is a GaN layer. The light emission layer 12 is a multiple quantum well layer with InGaN and GaN. The peak wavelength of light emitted from the light emission layer 12 is 450 nm.

**[0118]** FIG. 4(a) is an aerial view of the micro light emitting element having a rectangular parallelepiped structure. FIG. 4(b) is an aerial view of the micro light emitting element 100 having a truncated bent pyramid type structure according to Embodiment 1 of the present invention. The micro light emitting element having the rectangular parallelepiped structure illustrated in FIG. 4(a) and the micro light emitting element 100 having a truncated bent pyramid type structure illustrated in FIG. 4(b) according to Embodiment 1 of the present invention were compared to each other.

[0119] In all cases of FIG. 4(a) and FIG. 4(b), the size of the upper surface of the N-side layer 11 was 8  $\mu$ m×8  $\mu$ m, and the same compound semiconductor was used. In the cases of FIG. 4(a) and FIG. 4(b), the constituent materials and the formation processes are the same as each other except for a different shape. In the case of FIG. 4(a), the separation trench and the isolation trench were processed to be inclined as small as possible.

[0120] In all the cases, a transparent resin layer containing a scattering material was disposed on the upper surface of the N-side layer. In addition, in all the cases, 10000 pieces of micro light emitting elements in 100 rows×100 columns were simultaneously turned on, so as to evaluate total luminous flux intensity. The current amount per one micro light emitting element 100 is 5  $\mu A$ . The following Table 1 shows measurement results.

TABLE 1

|                                                                                 | Rectangular<br>parallelepiped<br>structure | Truncated bent pyramid type structure |

|---------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------|

| External quantum efficiency                                                     | 12%                                        | 43%                                   |

| Area ratio of light emission layer                                              | 100%                                       | 32%                                   |

| to light emitting surface<br>Estimated effective internal<br>quantum efficiency | 66%                                        | 53%                                   |

[0121] As shown in Table 1, in the truncated bent pyramid type structure in FIG. 4(b), external quantum efficiency is 3.6 times that of the simple rectangular parallelepiped structure in FIG. 4(a). In the truncated bent pyramid type structure in FIG. 4(b), even though the area of the light emission layer is about  $\frac{1}{3}$  of the area of the rectangular parallelepiped structure in FIG. 4(a), large improvement is achieved. To investigate root cause of the improvement, the light extraction efficiency was simulated with a lay trace method. The following Table 2 shows results. Estimated effective internal quantum efficiency in Table 1 is an estimated value obtained by being calculated from the external quantum efficiency in Table 1 with the light extraction efficiency in Table 2. Values shown in Table 2 are simulation values.

TABLE 2

|                                    | Rectangular<br>parallelepiped<br>structure | Truncated bent pyramid type structure |

|------------------------------------|--------------------------------------------|---------------------------------------|

| Light extraction efficiency        | 17.9%                                      | 80.7%                                 |

| Side surface absorption            | 29.4%                                      | 8.8%                                  |

| Bottom surface absorption          | 29.5%                                      | 6.0%                                  |

| Internal absorption                | 23.2%                                      | 4.5%                                  |

| Average internal reflection number | 85.4                                       | 25.4                                  |

[0122] The light extraction efficiency indicates a proportion of the quantity of light emitted from the upper surface of the micro light emitting element into the transparent resin layer. Side surface absorption indicates a proportion of the quantity of light absorbed by the metal reflective layer 20W on the entire side surface of the micro light emitting element. Bottom surface absorption indicates a proportion of the quantity of light absorbed by the P-side metal layer 10 on the lower surface of the micro light emitting element. Internal absorption indicates a proportion of the quantity of light absorbed again by the light emission layer 12. The average internal reflection number indicates an average of reflections in the compound semiconductor 14 until light emitted from the light emission layer 12 is emitted to the outside or is absorbed by the metal reflective layer 20W.

[0123] The tendency of the light extraction efficiency in Table 2 coincides well with the tendency of the external quantum efficiency in Table 1. It is considered that a difference in external quantum efficiency is the main cause of a difference in light extraction efficiency. Only light incident to the upper surface of the micro light emitting element at an angle which is equal to or less than a critical total reflection angle is emitted to the outside from the upper surface of the micro light emitting element. The critical total reflection angle is about 37° in a case of light which is incident from GaN to the transparent resin layer.

[0124] In the rectangular parallelepiped structure in FIG. 4(a), an incident angle to the upper surface of the micro light emitting element is constant regardless of the number of reflections therein. Thus, light emitted from the light emission layer 12 in a horizontal direction is not emitted to the outside. On the contrary, in the truncated bent pyramid type structure in FIG. 4(b), light emitted from the light emission layer 12 in the horizontal direction is reflected upward by the slope 16S, is incident to the light emitting surface at an angle of the critical total reflection angle or less, and then is emitted to the outside.

[0125] Further, even in a case where light is not emitted to the outside in an initial state when the light is emitted from the light emission layer 12, every time the light is reflected by the N-side layer side surface 11S, the incident angle of the light to the upper surface of the micro light emitting element 100 changes.

[0126] Therefore, light emitted from the light emission layer 12 repeats internal reflection, and then is emitted to the outside. Accordingly, it is possible to significantly improve the light extraction efficiency.

[0127] Next, in order to examine an influence of the transparent insulating film 17, dependency of the light extraction efficiency on the film thickness of the transparent insulating film 17 in the micro light emitting element 100 according to one form of the present invention was simulated. FIG. 5 illustrates results in a case of using SiO<sub>2</sub> as the transparent insulating film 17. FIG. 5 is a diagram illustrating a simulation result of film thickness dependency on the transparent insulating film 17 at the light extraction efficiency.

[0128] In FIG. 5, a horizontal axis indicates the film thickness, and a vertical axis indicates light extraction efficiency. In a case where the transparent insulating film 17 is not provided, the light extraction efficiency is 63%. Thus, in the truncated bent pyramid type structure in which the transparent insulating film 17 is not provided, light extraction efficiency is much larger than that of the rectangular parallelepiped structure with the transparent insulating film 17. It is shown that the shape of the compound semiconductor 14 is very important.

[0129] The light extraction efficiency increases as the film thickness of the transparent insulating film 17 becomes thicker. However, in a case where the film thickness of the transparent insulating film 17 is equal to or more than 400 nm, the change is small. Thus, it is most preferable that the film thickness of the transparent insulating film 17 is equal to or more than 400 nm. Since the decrease rate of the light extraction efficiency is within 5% if the film thickness is equal to or more than 75 nm, the film thickness may be equal to or more than at least 75 nm.

[0130] As the effect by the transparent insulating film 17, it is considered to improve reflectivity on the side surface of the micro light emitting element 100 and to improve the light extraction efficiency. In the rectangular parallelepiped structure, the effect by the transparent insulating film 17 is very weak. The reason is considered as follows. Even though the reflectivity on the side surface of the micro light emitting element having the rectangular parallelepiped structure is improved, the angle incident to the upper surface of the micro light emitting element is not changed. Thus, light which is totally reflected by the upper surface is always reflected no matter how many times the light is reflected at side surfaces, and the light extraction efficiency is not

improved. Thus, it is important that the micro light emitting element 100 has the slope 16S and the inclined N-side layer side surface 11S which allow the incident angle to the upper surface to change.

[0131] Next, FIG. 6 illustrates results obtained by examining the change of the light extraction efficiency to the dimensions and the angles of each unit in the micro light emitting element 100 with the simulation. FIGS. 6(a) to 6(e) are diagrams illustrating simulation results of dependency of the light extraction efficiency on the dimensions and the angles of each unit in the image display element 200 illustrated in FIG. 1(a). FIGS. 6(a) to 6(e) also illustrate ratios (area ratio) of the area of the light emission layer 12 to the area of the light emitting surface (upper surface of the N-side layer 11). In FIGS. 6(a) to 6(e), a vertical axis indicates the light extraction efficiency or the area ratio.

[0132] In all cases in FIGS. 6(a) to 6(e), so long as particular statements are not made, the size of the upper surface of the N-side layer 11 is  $8 \mu m \times 8 \mu m$ , the thickness of the N-side layer 11 is  $6 \mu m$ , and the thickness of the P-side layer 13 is  $0.1 \mu m$ . In addition, the inclined angle  $\theta e$  of the slope 16S is 500, the depth D at the portion occupied by the N-side layer 11 in the slope 16S is  $1 \mu m$ , and the inclined angle  $\theta e$  of the N-side layer side surface 11S is 800.

[0133] FIG. 6(a) illustrates dependency of the light extraction efficiency on the inclined angle  $\theta b$  of the N-side layer side surface 11S. In FIG. 6(a), a horizontal axis indicates the inclined angle  $\theta b$ . As illustrated in FIG. 6(a), as the inclined angle  $\theta b$  of the N-side layer side surface 11S becomes smaller, the light extraction efficiency is improved. Preferably, the inclined angle  $\theta b$  of the N-side layer side surface 11S is equal to or less than 83°.

[0134] FIG. 6(b) illustrates dependency of the light extraction efficiency on the depth D at the portion occupied by the N-side layer 11 in the slope 16S. In FIG. 6(b), a horizontal axis indicates the depth D. As illustrated in FIG. 6(b), as the depth D increases, the light extraction efficiency is improved. Preferably, the depth D is equal to or more than  $0.6 \mu m$ .

[0135] FIG. 6(c) illustrates dependency of the light extraction efficiency on the inclined angle  $\theta$ e of the slope 16S. In FIG. 6(c), a horizontal axis indicates the inclined angle  $\theta$ e. In order to improve the light extraction efficiency, the inclined angle  $\theta$ e is preferably equal to or less than 600, and further preferably equal to or less than 500. FIG. 6(d) illustrates dependency of the light extraction efficiency on the thickness of the N-side layer 11. The thickness is a thickness in the vertical direction (direction from the upper surface of the micro light emitting element 100 toward the lower surface). In FIG. 6(d), a horizontal axis indicates the thickness of the N-side layer 11. As the thickness of the N-side layer 11 becomes thicker, the light extraction efficiency is improved. The thickness of the N-side layer 11 is preferably equal to or more than 3  $\mu$ m.

[0136] FIG. 6(e) illustrates dependency of the light extraction efficiency on the thickness of the P-side layer 13. In FIG. 6(e), a horizontal axis indicates the thickness of the P-side layer 13 becomes thicker, the light extraction efficiency is improved. However, the influence is smaller than those of other parameters illustrated in FIGS. 6(a) to 6(d).

[0137] With the drawings, the micro light emitting element 100 according to one form of the present invention can realize light extraction efficiency which is equal to or more

than at least 48%. This exhibits very large improvement of about 2.7 times the light extraction efficiency in the rectangular parallelepiped structure, which is shown in Table 2. Further, in the micro light emitting element 100 according to the one form of the present invention, it is possible to realize the light extraction efficiency of 70% or more by appropriately selecting the structure of the micro light emitting element 100.

[0138] In the micro light emitting element 100 according to the one form of the present invention, the entire periphery of the side surface of the light emission layer 12 is configured as the portion of the slope 16S, and the N-side layer side surface 11S from the slope 16S to the upper surface of the N-side layer 11 is inclined by an angle larger than the angle of the slope 16S. In addition, in the micro light emitting element 100, the slope 16S and the N-side layer side surface 11S are covered by the metal reflective layer 20W

[0139] Thus, it is possible to prevent the occurrence of optical crosstalk between the micro light emitting elements 100 and to significantly improve the light extraction efficiency. Further, since the transparent insulating film 17 is disposed between the slope 16S and the N-side layer side surface 11S, and the metal reflective layer 20W, it is possible to further improve the light extraction efficiency.

#### Embodiment 2

[0140] (Configuration of Image Display Element 200a) Another embodiment of the present invention will be described below with reference to FIGS. 7 and 8. For easy description, members having the same functions as the members described in the above embodiment are denoted by the same reference signs, and repetitive descriptions thereof will not be made. An image display element 200a in Embodiment 2 is different from the image display element 200 in Embodiment 1 in that sticking between the driving circuit substrate 50 and the micro light emitting element 100a is performed in a manner of wafer-to-wafer bonding. The wafer-to-wafer bonding has an advantage in that generation of dust is suppressed, and high yield is realized.

[0141] FIG. 7 is a schematic sectional view of the image display element 200a according to Embodiment 2 of the present invention. Differing from the micro light emitting element 100, a micro light emitting element 100a is buried by an insulating film 21, and a surface of the micro light emitting element 100a on an opposite side of the light emitting surface is flat. The micro light emitting element 100a and the driving circuit substrate 50 are stuck to each other on a flat bonding surface. A P-damascene electrode 23P and an N-damascene electrode 23N in the micro light emitting element 100a are bonded to the P-drive electrode 51 and the N-drive electrode 52 on the driving circuit substrate 50, respectively.

[0142] As described later, the P-damascene electrode 23P and the N-damascene electrode 23N are formed by the same process. Thus, the P-damascene electrode and the N-damascene electrode are formed of the same wiring material regardless of the different shape, size, and depth. That is, the P-damascene electrode 23P and the N-damascene electrode 23N have the same stacked structure including a barrier metal layer, a main conductive layer, a cap layer, and the like. Lower surfaces of the P-damascene electrode 23P and the N-damascene electrode 23N are configured in substantially the same plane as the lower surface of the insulating

film 21. The structure except for the above description is similar to that of the image display element 200 in Embodiment 1.

[0143] The surface of the insulating film 55 (on the driving circuit substrate 50 side) on the bonding surface side is also flat, and upper surfaces of the P-drive electrode 51 and the N-drive electrode 52 are configured in substantially the same plane as the upper surface of the insulating film 55. A slight difference in height may be provided between the lower surface of the insulating film 21, and the lower surfaces of the P-damascene electrode 23P and the N-damascene electrode 23N, so long as sticking of the micro light emitting element 100a and the driving circuit substrate 50 is possible. This is similarly applied to a difference in height between the upper surface of the insulating film 55 on the driving circuit substrate 50 side, and the upper surfaces of the P-drive electrode 51 and the N-drive electrode 52.

[0144] Normally, a layer constituting the lower surfaces of the P-damascene electrode 23P and the N-damascene electrode 23N has the same material as that of a layer constituting the upper surfaces of the P-drive electrode 51 and the N-drive electrode 52. Examples of the material of the above layers include gold (Au), copper (Cu), and nickel (Ni).

[0145] (Manufacturing Flow of Image Display Element 200a)

[0146] FIGS. 8(a) to 8(d) are schematic sectional views illustrating a manufacturing flow of the image display element 200a according to Embodiment 2 of the present invention. In descriptions of the manufacturing flow of the image display element 200a in FIGS. 8(a) to 8(c), the insulating film 21 side is set to be upper, and the growth substrate 9 side is set to be lower. In descriptions of the manufacturing flow of the image display element 200a in FIG. 8(d), the growth substrate 9 side is set to be upper, and the driving circuit substrate 50 side is set to be lower.

[0147] FIG. 8 illustrates only the pixel region 1 and the N connection region 3 of an image display element 200a, but the manufacturing flow of the image display element 200a is not performed for each image display element 200a. In the manufacturing flow of the image display element 200a, preferably, a plurality of image display elements 200a are manufactured at a time by sticking a wafer for a plurality of driving circuit substrates 50 and a wafer for a plurality of micro light emitting elements 100a to each other.

[0148] A portion of the manufacturing flow of the micro light emitting element 100a is the same as the processes for the micro light emitting element 100, which are illustrated in FIGS. 2(a) to 2(g). In the manufacturing flow of the micro light emitting element 100a, after the metal layer 20 is patterned as illustrated in FIG. 8(a), the insulating film 21 is deposited to cover the exposed portions of the P-electrode 20P, the transparent insulating film 17, and the metal reflective layer 20W.

[0149] After the insulating film 21 is deposited, the upper surface of the insulating film 21 is flattened by a chemical-mechanical-polishing (CMP) method. The insulating film 21 is, for example, a film of SiO<sub>2</sub>, SiN, SiON or a film obtained by stacking these film. Various film formation technologies such as a chemical vapor deposition (CVD) method, a sputtering method, and a coating method can be used for forming the insulating film 21.

[0150] After the insulating film 21 is flattened, as illustrated in FIG. 8(b), a P-trench 22P and an N-trench 22N are formed in the insulating film 21 on the P-electrode 20P and

the N-electrode 20N, respectively. The P-trench 22P has a hole shape and reaches the P-electrode 20P. The N-trench 22N has a hole shape or a line shape and reaches the N-electrode 20N.

[0151] After the P-trench 22P and the N-trench 22N are formed, as illustrated in FIG. 8(c), the P-damascene electrode 23P and the N-damascene electrode 23N are formed by burying a metal film in the P-trench 22P and the N-trench 22N with a damascene method. The metal film is, for example, a combination of copper and a barrier film of tantalum (Ta), tungsten (W), and titanium nitride (TiN). The metal film may be a combination of gold (Au), nickel (Ni) or the like with the corresponding barrier film.

[0152] In the damascene method, a metal thin film is deposited on an underlying structure having a trench, and the metal thin film is polished by a CMP method. Thus, the metal thin film can remain in the trench, and the upper surface of the underlying structure is level with the upper surface of the metal thin film. In the above-described manner, the P-damascene electrode 23P is disposed on the P-electrode 20P, and the N-damascene electrode 23N is disposed on the N-electrode 20N. The P-damascene electrode 23P and the N-damascene electrode 23P and the N-damascene electrode 23N are configured with the same material. The upper surface of each of the P-damascene electrode 23P and the N-damascene electrode 23N are level with the surface, which functions as the bonding surface to the driving circuit substrate 50.

[0153] After the P-damascene electrode 23P and the N-damascene electrode 23N are formed, as illustrated in FIG. 8(d), the micro light emitting element 100a and the dummy connection element 101a are stuck to the driving circuit substrate 50. At this time, the P-damascene electrode 23P and the N-damascene electrode 23N are precisely aligned to overlap with the corresponding P-drive electrode 51 and N-drive electrode 52, respectively.

[0154] Two wafers are stuck to each other by plasma cleaning of the surface, activation by ion irradiation, heating, and pressurization, in accordance with the material of the bonding surface between the micro light emitting element 100a and the dummy connection element 101a, and the driving circuit substrate 50. In the subsequent processes, similar to the processes illustrated in FIGS. 3(c) to 3(e), the growth substrate 9 is removed, and the common N-electrode 40 is formed. In the manufacturing flow of the micro light emitting element 100a, since the insulating film 21 is deposited between the micro light emitting elements 100a, the filling material 60 is not required.

[0155] In the configuration of the image display element 200a, the periphery of the micro light emitting element 100a is covered by the metal reflective layer 20W. Thus, even though the transparent insulating film is deposited between the micro light emitting elements 100a, the occurrence of light leakage between the micro light emitting elements 100a adjacent to each other is prevented. Thus, even though an insulating film such as  $SiO_2$ , which is generally used, is used, it is possible to prevent an occurrence of a problem that contrast and color purity are degraded.

[0156] As described above, since the wafers are stuck to each other, it is possible to reduce dust generation and to realize high yield. For example, if the micro light emitting elements are divided in a unit of the image display element, a large amount of dust is generated in the division process. Thus, a problem that the yield is significantly decreased by the bonding occurs, because the dusts are adhered to the

bonding surface in a process of sticking the micro light emitting element to the driving circuit substrate.